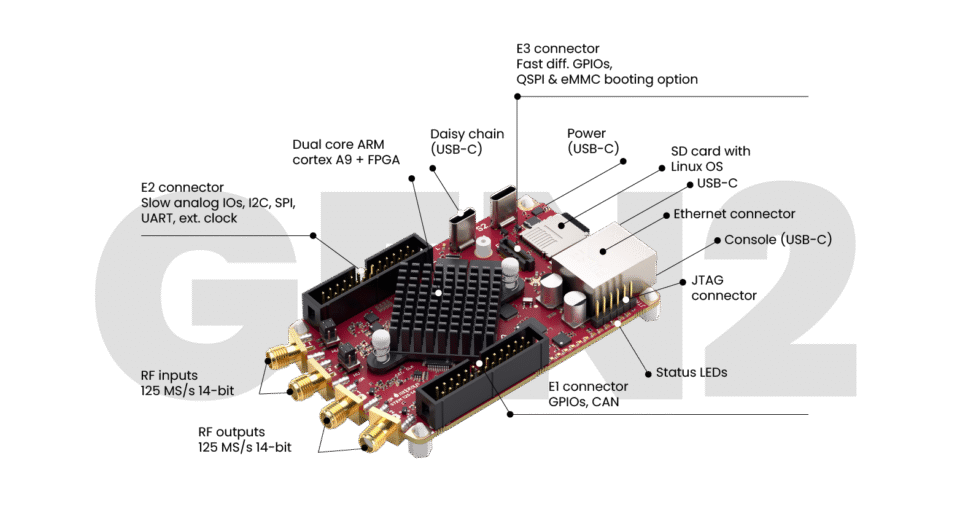

A full-cycle hardware, FPGA and embedded software development project for a customer Red Pitaya, delivered in 12 months.

To meet growing demands for performance, modularity, and long-term component viability, Red Pitaya initiated development of the second generation of its popular STEMlab 125-14.

The requirements were defined based on the available state-of-the-art components and PCB manufacturing abilities, market needs, and customer’s suggestions.

THE PROJECT AIMED TO:

- Improve performance and latency of high-speed RF inputs/outputs

- Modernize the platform with newer components and technologies

- Maintain pin and software compatibility with Gen 1 for seamless user transition

- Introduce optional features via modular expansion

- Ensure long-term support and cost-effective manufacturing

Our engineering team was tasked with delivering end-to-end development all within the constraints of the original device’s form factor:

KEY CHALLENGES

- Performance upgrade driven by user needs, while maintaining the same form factor

- Integration of optional features without significally increasing baseline price

- Elimination of obsolete components

- Maintaining backward compatibility

- Preparing the system for scalable manufacturing and testing