# Extensions and common points of the platform C instruments

Peter Leban, June 1, 2017

www.i-tech.si

# Content

Platform C hardware

Common hardware

Extension modules

Common software

Conclusion

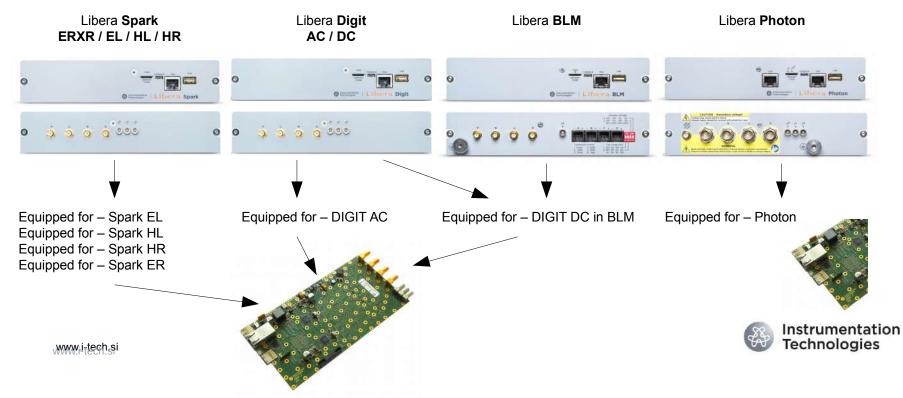

## Platform C hardware

#### Common hardware points

3x Input / output LEMO

4 channels with various assembly options

Zynq 7020

www.i-tech.si

2x dual channel ADC

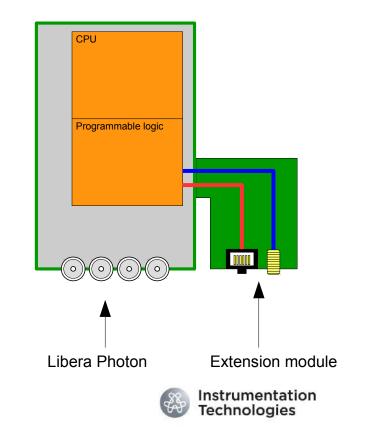

Extension slot

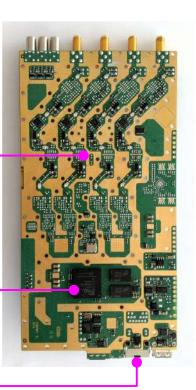

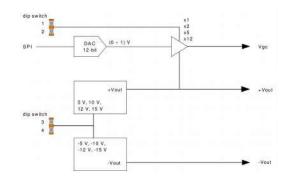

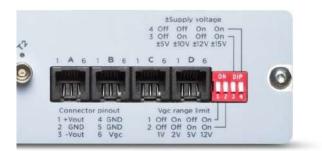

### Extension module for BLM

- 4x RJ25 interface

- DIP switch

- Power supply and gain control for the PMTs

- Direct control from Zynq (FPGA and OS)

# Extension module for Photon (not developed yet)

- To offer analog output for feedback purposes

- Planned from design phase, instrument can be upgraded, space was allocated already

- Type of connector (SMA, BNC, LEMO?) and DAC still to be specified

- Space available for 2 connectors (e.g. SMA and RJ-25); serial data output possible as well

- Data pins directly controlled by the Programmable Logic (FPGA) from Zynq

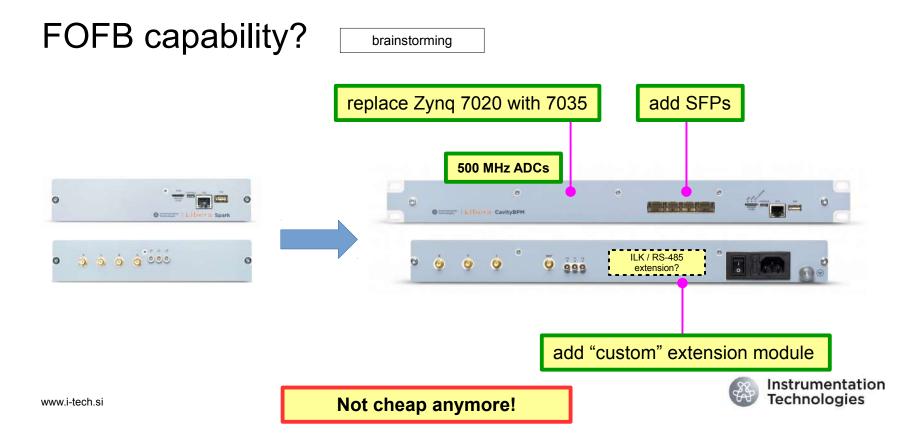

# (Hardware) updates for platform C

Users asked for

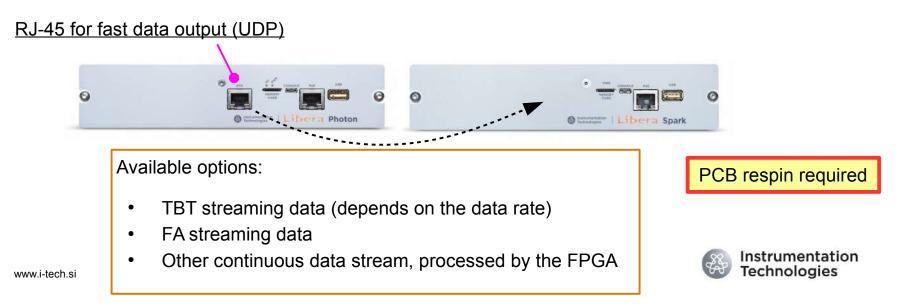

- Fast data output (additional dedicated interface)

- Different ADC sensitivity

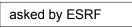

- Interlock capability

- Several modifications in <u>ebpm</u>, <u>blm</u> and <u>photon</u> applications

for energy ramping application

"oscilloscope" features

for beam profile monitors

for Spark ERXR

era

### Fast data output asked by ESRF, APS

It is available in Libera Photon. The PCB is slightly different from the BLM, Spark and Digit

pera

i

### ADC sensitivity

It is configured during assembly. For the future, it could be done runtime by user.

Available options:

- 0.5 V full scale

- 1.0 V full scale

PCB respin required

## Interlock capability asked by Cornell

#### Typical use (all configured as inputs)

- T0 ... reference clock (»tbt«)

- T1 ... postmortem trigger

- T2 ... (acquisition) trigger

#### Interlock output on the extension module

- Interlock functionality implementation (FPGA, software)

- Use same circuit as on the Libera Electron / Brilliance / +

pera

# Libera

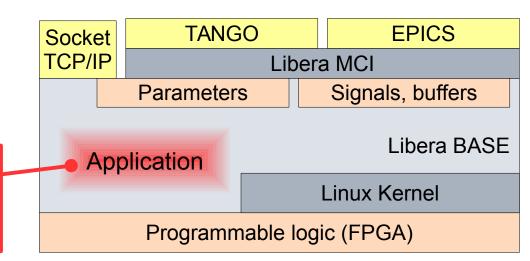

# Software

- Support for most devices in the general framework: Libera BASE Continuously developed, currently builds for lucid (32/64), trusty (32/64), CentOS and Zynq Interfaces to latest ADCs (500 MHz) and FPGA (Zynq 7035)

- Client application is backward compatible (MCI)

- New application does not interfere (unless required) with the Libera BASE

- EPICS, TANGO and Socket interfaces are cross-platform compatible

# Common software points

- FPGA cores

- Libera BASE

- EPICS interface

- TANGO interface

- \*Socket TCP/IP interface

Application (digit, beam loss, bpm) is <u>custom</u> but uses common blocks.

## (I-Tech's) TANGO interface

#### ...is called libera-ds

- Initial version installed in Libera Brilliance+ (THOM-X)

- Improved version then installed on Libera BLM (ESRF) and Libera Spark EL (ALBA)

- Further debugging by THOM-X and ESRF; latest updates provided by ESRF

- Same code compiled for Ubuntu lucid/trusty and Zynq Linux

- ... to be continued

era

## (I-Tech's) EPICS interface

- ...is called libera-ioc

- Several updates since year 2010 (from CA server to IOC)

- Using I-Tech's patched EPICS BASE 3.14.12.2 for optimal CPU consumption

- ... complaints / requirements from NSRL, NSRRC and APS

- Migration to the official EPICS BASE 3.15.5; currently under testing at NSRRC and APS

- Requires smarter handling of buffer readout (disable when not in use)

- All use cases not known; yet to be improved

### Socket TCP/IP interface

#### ...is called libera-scpi

- Bypasses the MCI layer; direct calls to the Libera BASE

- SCPI-like commands

- Tested in MATLAB environment

- ...to be further expanded

www.i-tech.si

```

format longG

t=tcpip('10.0.6.114',5677,'NetworkRole','client')

t.InputBufferSize=100000

fopen(t)

fprintf(t,'dump')

data=fread(t, 27)

while t.BytesAvailable > 0

data=fscanf(t,'%c',t.BytesAvailable)

%strread(data)

str2num(data)

end

fclose(t)

```

# Libera

# Conclusion

- Many instruments based on the same PCB

- Extension slot available for various modules

- Common software framework allows fast development cycles

- Platform upgrade possible with use of faster A/D converters