### **Borut Repič**

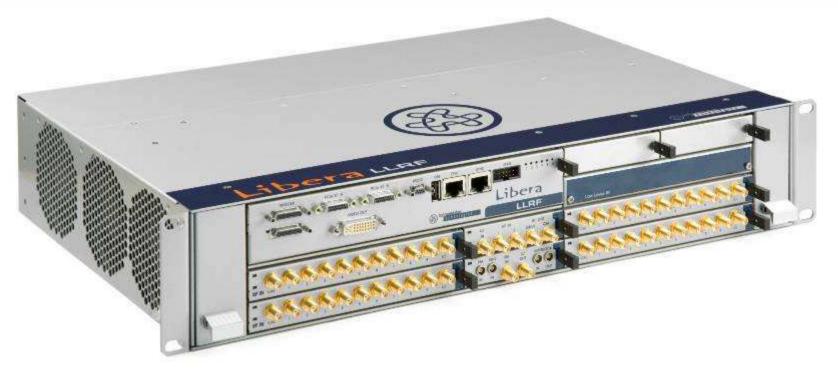

## Libera LLRF

borut@i-tech.si

13. October 2008

## Libera LLRF system

Digital RF stabilization system:

all-in-one,

customizable,

ready to integrate in the control system

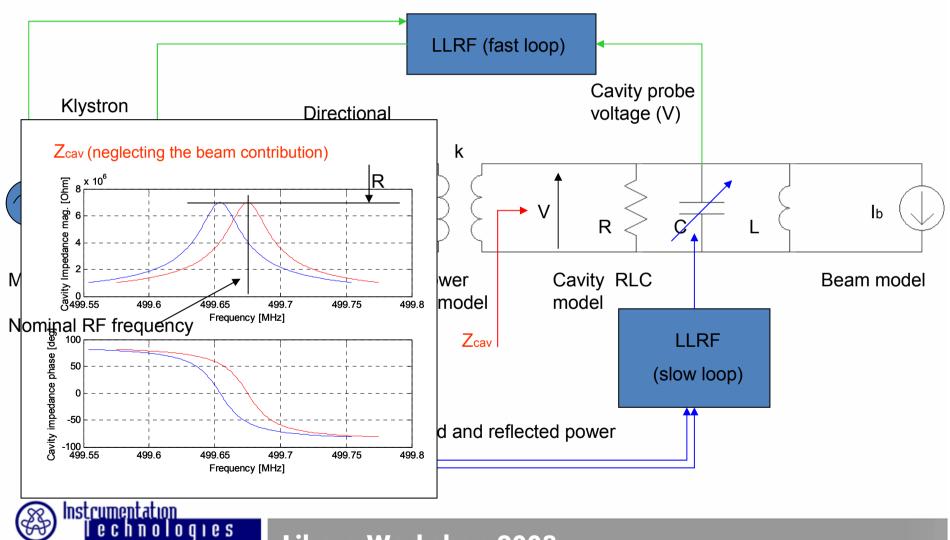

### RF cavity ("Elettra" 500 MHz, Q=42000)

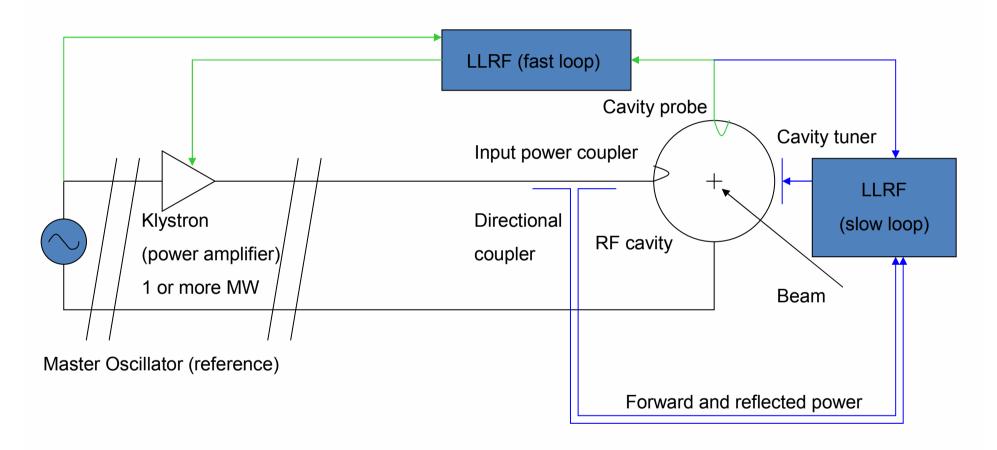

## RF system & LLRF

## LLRF and cavity-beam model

## **LLRF** system

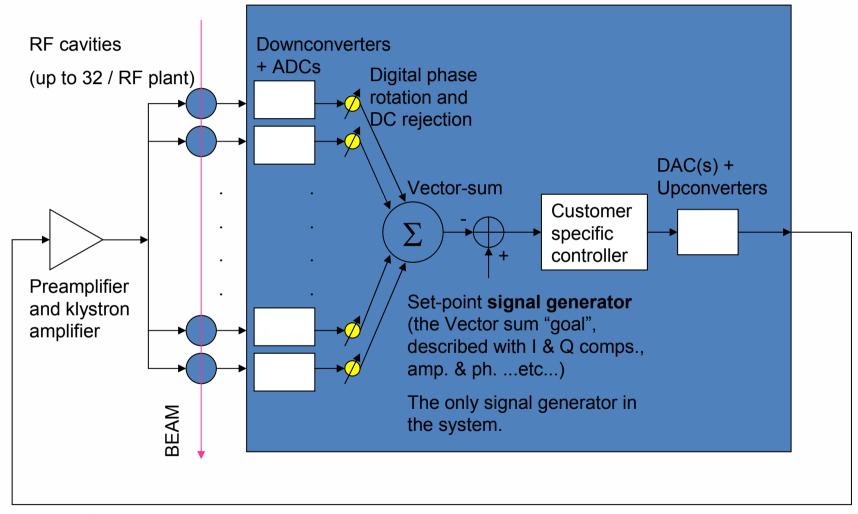

LLRF System (implementing the cavity field stabilization)

## RF system characteristics

- 1) SuperConducting vs. NormalConducting RF systems:

- NC: EMMA: RF freq. 1.3 GHz, BW=56 kHz, Q=23000

- SC: XFEL: RF freq. 1.3 GHz, BW=100 Hz, Q=13E6 (sophisticated tuning system (piezo))

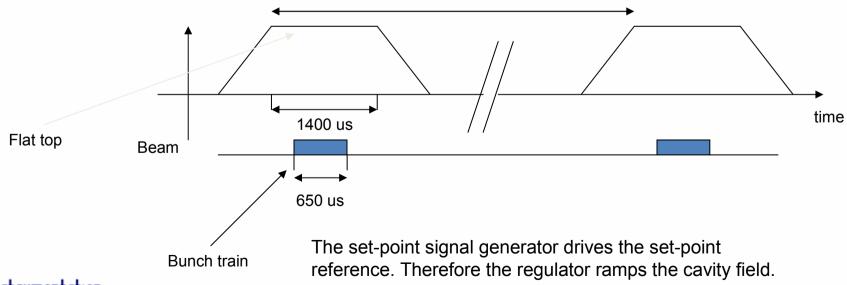

- 2) Pulsed vs. CW:

- CW: RF field on all the time (storage rings)

- Pulsed systems: RF field active during a limited period of time (few ms) repetition rates from 10 Hz to 100 Hz

### **ALL-IN-ONE / Integrated**

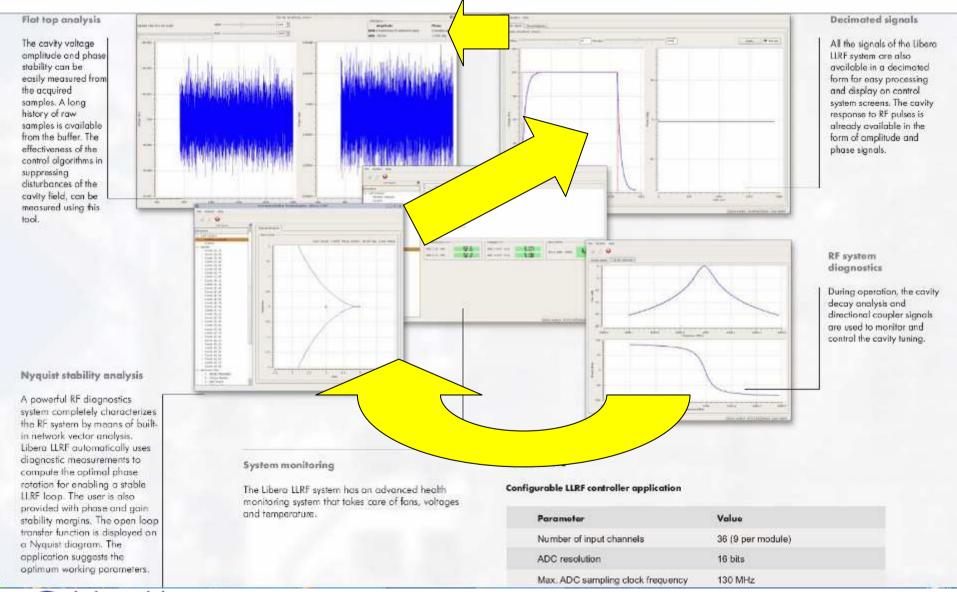

The all-in-one unit replaces a field of different instruments and crates:

- Built-in RF system diagnostics: automatic phase and gain correction, cavity field control loop stability analysis, cavity decay analysis monitoring

- Cavity tuning included

- Cavity field stabilization: jitter cancellation, vector sum alignment, calibration system, computation of the cavity field vector sum, cavity field control by means of a programmable PI controller, feed-forward system

- Built-in interlock system

- Self calibration

- Chassis health monitoring

- Built-in local oscillator generation

# SUITABLE FOR THE LATEST GENERATION LIGHT SOURCES and HADRON

able controller; easy upgradeable

era LLRF field programmable gate

e RF Input frequency up to 12 GHz

ites fast signal processing and logic

pre-built blocks that interfaces lware, it is possible to customize the

our specific needs

oment kit available

rity signals per station

- Phase and amplitude stability meets 4th generation light sources' requirements

- Compatible with normal-conducting and superconducting RF systems

- Supports pulsed and continuous wave operation modes

- Low latency

**ACCELERATORS**

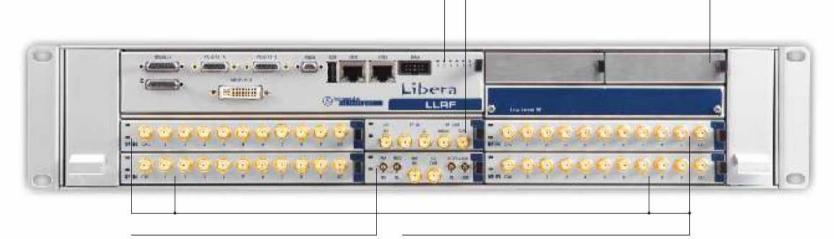

### Hardware Interfaces

### Intel dual core COM Express with extensive communication interfaces:

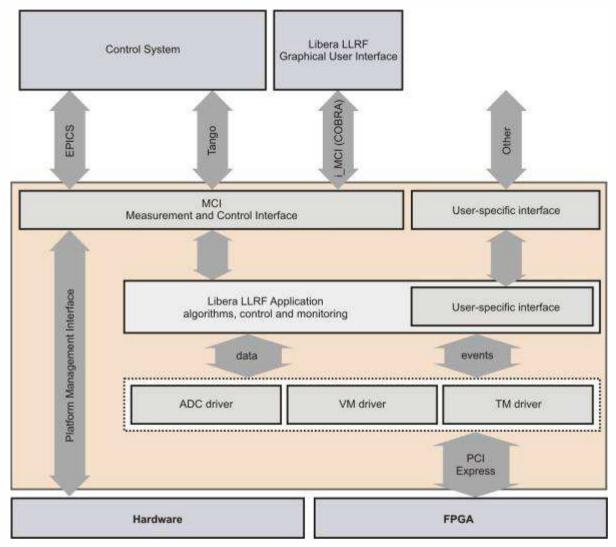

The latest FPGAs and a powerful personal computer based on the PCIe interface offer good resources for the implementation of low-latency control algorithms, real-time data processing and dedicated RF system diagnostics tools.

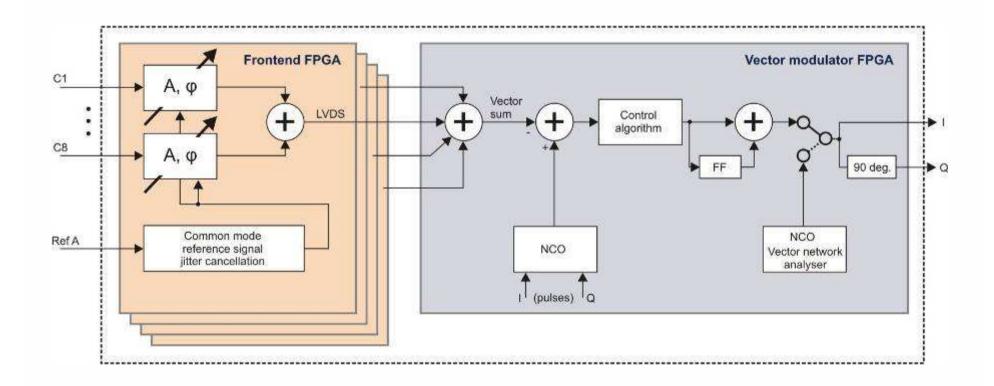

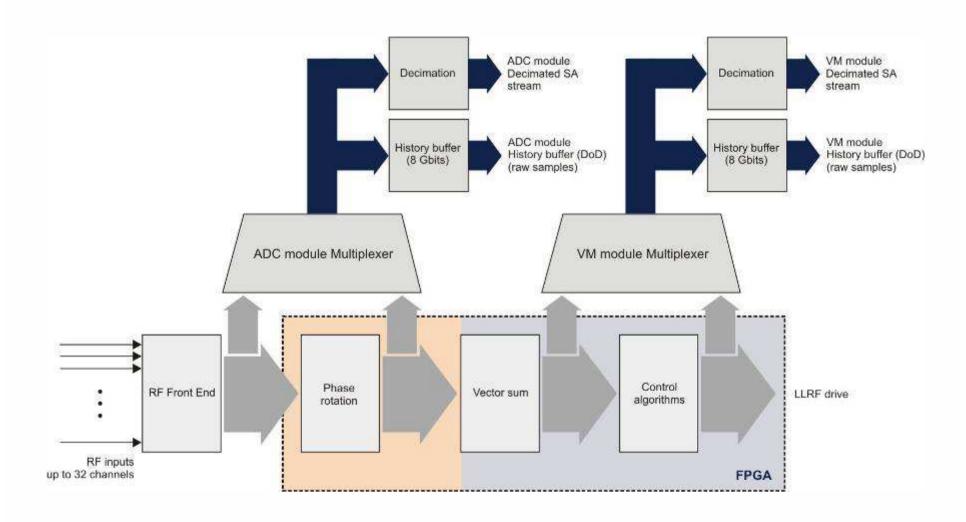

#### Vector modulator module:

Receives the partial vector sum signals from four satellite ADC modules through low-latency low-voltage differential signaling (LVDS) lines. The global vector sum is then processed by means of FPGA algorithms. The output of the control algorithms is then up-converted to the RF frequency and used as the transmitter drive signal.

Optional fast communication modules

### Timing module:

Generates a low jitter local oscillator (LO) signal and a suitable sampling clock for the down-conversion and acquisition processes. The designed acquisition structure enables a high level of amplitude and phase cavity field stabilization.

### RF acquisition modules:

The system is configured to have four satellite modules, each of which can process up to 9 RF inputs. One channel on each board is used as RF reference signal for measurement and jitter cancellation purposes. Each RF acquisition module includes a built-in calibration system, temperature stabilization, jitter cancellation, LO distribution, partial vector sum computation and vector sum phase alignment functions.

# LLRF signal levels

### ADC9:

-RF inputs 1-9: 20 dBm

-Cal. input : 20 dBm

-LO input : 0 dBm

TCM:

-Ref. Input : 0 dBm

-LO output : 18 dBm

VM:

-LO input : 0 dBm

-RF in : 20 dBm

-RF out : 12 dBm

### **Hardware Interfaces**

### Intel dual core COM Express with extensive communication interfaces:

The latest FPGAs and a powerful personal computer based on the PCIe interface offer good resources for the implementation of low-latency control algorithms, real-time data processing and dedicated RF system diagnostics tools.

#### Vector modulator module:

Receives the partial vector sum signals from four satellite ADC modules through low-latency low-voltage differential signaling (LVDS) lines. The global vector sum is then processed by means of FPGA algorithms. The output of the control algorithms is then up-converted to the RF frequency and used as the transmitter drive signal.

Optional fast communication modules

#### Timing module:

Generates a low jitter local oscillator (LO) signal and a suitable sampling clock for the down-conversion and acquisition processes. The designed acquisition structure enables a high level of amplitude and phase cavity field stabilization.

#### RF acquisition modules:

The system is configured to have four satellite modules, each of which can process up to 9 RF inputs. One channel on each board is used as RF reference signal for measurement and jitter cancellation purposes. Each RF acquisition module includes a built-in calibration system, temperature stabilization, jitter cancellation, LO distribution, partial vector sum computation and vector sum phase alignment functions.

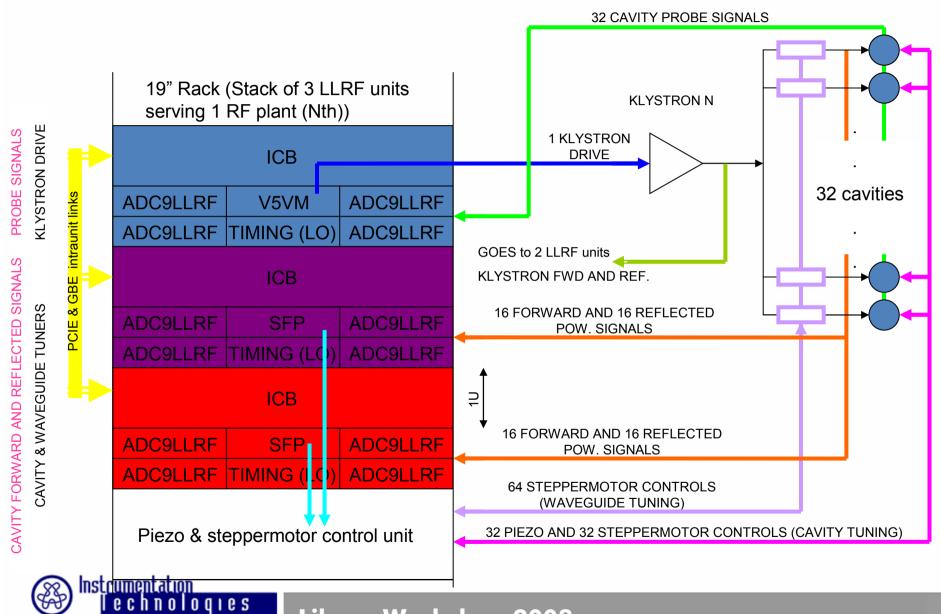

## Distributed processing

## Data paths

### **SW** interfaces

**GUI**

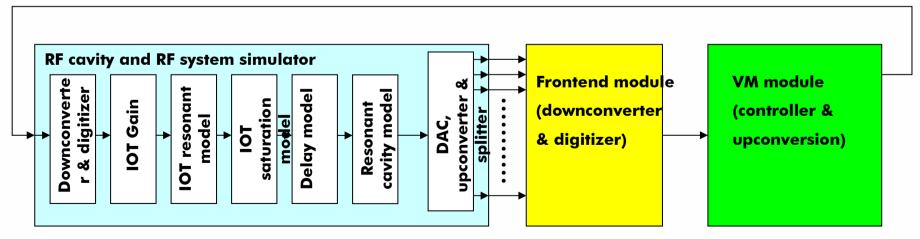

# **Cavity simulator**

Designed to model the CPI IOT power amplifier non linear effects, limited bandwidth and the EMMA NC cavity.

- Based on upconversion and downconersion chains + BBFP

- Nominal RF frequency 1.3 GHz

- Nominal BW= 56 kHz (Q=23000)

- IF frequency 100 MHz

- Sampling frequency for IF 350 MHz

- Conversion LO frequency: 1400 MHz

- other features: variable gain, phase, resonant frequency and group delay

# Libera LLRF performance

Input RF chain crosstalk (far end): - 70 dB

Crosstalk ratio at IF level: - 60 dB

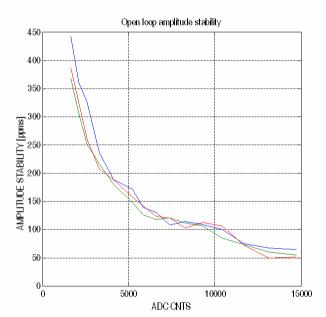

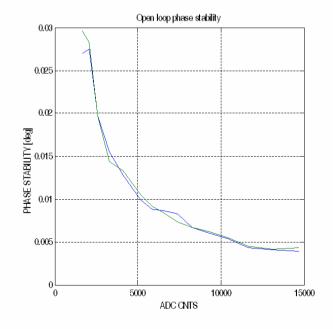

Open loop stability:

Amplitude: 0.007 %

Phase: 0.005 deg

Estimated latency: 200 ns

|       | -80.9 | -78.7 | -80.1 | -81.2 | -81.7 | -83.2 | -81.9 | -80.2 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| -73.3 |       | -73.3 | -82.1 | -80.9 | -81.7 | -82.5 | -82.7 | -79.7 |

| -79.9 | -69.2 |       | -83.7 | -78.4 | -80.8 | -82.4 | -82.5 | -80.1 |

| -81.7 | -81.4 | -72.7 |       | -73.4 | -79.1 | -80.8 | -82   | -80.6 |

| -81.1 | -82.8 | -80.8 | -73.4 |       | -76.7 | -79.2 | -79.7 | -78.4 |

| -82.4 | -83.5 | -82.4 | -80.6 | -76.4 |       | -79.8 | -77.2 | -77.5 |

| -82.3 | -84.5 | -82.9 | -82.2 | -82.8 | -70.5 |       | -83.8 | -76.9 |

| -81.1 | -83.8 | -83.8 | -82   | -82.5 | -79   | -71.1 |       | -88.5 |

| -80.3 | -81.8 | -82.6 | -80.7 | -79.5 | -83.4 | -80.2 | -70.7 |       |

## Thank you!

## XFEL LLRF example